TSMC создала улучшенную магниторезистивную память — она потребляет в 100 раз меньше энергии

Компания TSMC вместе с учёными Тайваньского НИИ промышленных технологий (ITRI) представила совместно разработанную память SOT-MRAM. Новое запоминающее устройство предназначено для вычислений в памяти и для применения в качестве кеша верхних уровней. Новая память быстрее DRAM и сохраняет данные даже после отключения питания, и она призвана заменить память STT-MRAM, потребляя при работе в 100 раз меньше энергии.

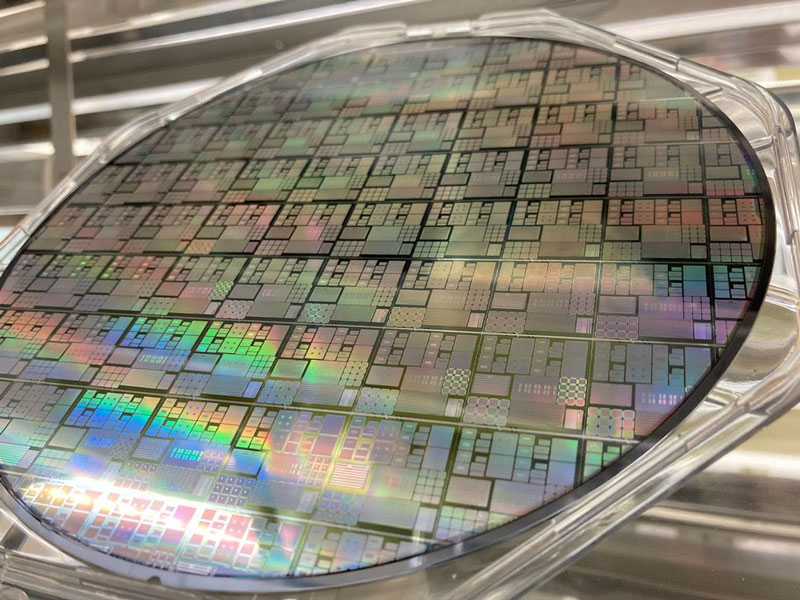

Экспериментальная пластина с чипами SOT-MRAM. Источник изображения: TSMC / ITRI

На роль кеш-памяти верхних уровней (от L3 и выше) и для вычислений в памяти, среди прочих перспективных вариантов энергонезависимой памяти, долгое время претендовала магниторезистивная память с записью с помощью переноса спинового момента (STT-MRAM). Этот вариант памяти передавал намагниченность запоминающей ячейке через туннельный переход с помощью спин-поляризованного тока. За счёт этого потребление энергии STT-MRAM оказалось кратно меньше потребления обычной памяти MRAM, в которой запись осуществлялась наведённым электромагнитным полем.

Память SOT-MRAM идёт ещё дальше. Запись (намагниченность) ячейки — слоя ферромагнетика — происходит с помощью спин-орбитального вращательного момента. Эффект проявляется в проводнике в основании ячейки в процессе комбинации двух явлений: спинового эффекта Холла и эффекта Рашбы—Эдельштейна. В результате на соседний с проводником ферромагнетик воздействует индуцированное магнитное поле со стороны спинового тока в проводнике. Это приводит к тому, что для работы SOT-MRAM требуется меньше энергии, хотя настоящие прорывы ещё впереди.

Маршруты токов записи и чтения для двух типов ячеек MRAM. Источник изображения: National University of Singapore

Другие преимущества памяти SOT-MRAM заключаются в раздельных схемах записи и чтения, что положительно сказывается на производительности, а также увеличенная устойчивость к износу.

«Эта элементарная ячейка обеспечивает одновременное низкое энергопотребление и высокоскоростную работу, достигая скорости до 10 нс, — сказал доктор Ши-Чи Чанг, генеральный директор исследовательских лабораторий электронных и оптоэлектронных систем ITRI. — Её общая вычислительная производительность может быть дополнительно повышена при реализации схемотехники вычислений в памяти. Заглядывая в будущее, можно сказать, что эта технология обладает потенциалом для применения в высокопроизводительных вычислениях (HPC), искусственном интеллекте (AI), автомобильных чипах и многом другом».

Память SOT-MRAM с задержками на уровне 10 нс оказывается ближе к SRAM (задержки до 2 нс), чем обычная память DRAM с задержками до 100 нс и выше. И конечно, она существенно быстрее популярной сегодня 3D NAND TLC с задержками от 50 до 100 мкс. Но в процессорах и контроллерах память SOT-MRAM появится не завтра и не послезавтра, как не стала востребованной та же память STT-MRAM, которая разрабатывается свыше 20 лет. Всё это будущее и не очень близкое, хотя, в целом, необходимое для эффективных вычислений в памяти и устройств с автономным питанием.

Источник: 3dnews.ru